Comparator fast

Author: m | 2025-04-25

Comparative and Superlative Degree of Fast Comparative degree of fast is faster and Superlative degree of fast is fastest. Here is the comparative and superlative degree for fast. Adjective Comparative Superlative Fast faster fastest Examples Using Positive Degree of Fast: The fast car zoomed down the highway. She ran at a fast pace in the marathon. The cheetah Ultra Fast Comparator Analog Comparators are available at Mouser Electronics. Mouser offers inventory, pricing, datasheets for Ultra Fast Comparator Analog Comparators.

Interdesigner.com: Comparator Fast - File Comparator

Design of Analog CMOS Integrated Circuits; Mc-Graw Hill Inc.: New York, NY, USA, 2015. [Google Scholar]Hesham, O. Fast and accurate technique for comparator offset voltage simulation. Microelectron. J. 2019, 89, 91–97. [Google Scholar]Peng, X.; Gao, A.; Chen, Z.; Zhang, H.; Li, Y.; Cao, W.; Liu, X.; Tang, H. A Novel Comparator Offset Calibration Technique for SAR ADCs. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018. [Google Scholar]Zhang, Y.; Cai, J.; Li, X.; Zhang, Y.; Su, B. A 3.66 μW 12-bit 1 MS/s SAR ADC with mismatch and offset foreground calibration. Microelectron. J. 2021, 116, 105–244. [Google Scholar] [CrossRef] Figure 1. The structure of the proposed self-calibration comparator applied in an SAR ADC system. Figure 1. The structure of the proposed self-calibration comparator applied in an SAR ADC system. Figure 2. The common-mode buffer. Figure 2. The common-mode buffer. Figure 3. The symmetrical OTA. Figure 3. The symmetrical OTA. Figure 4. Differential preamplifier Ai (i = 0, 2, …, 5, 6). Figure 4. Differential preamplifier Ai (i = 0, 2, …, 5, 6). Figure 5. Comparator offset cancellation techniques: (a) the output offset storage; (b) the input offset storage. Figure 5. Comparator offset cancellation techniques: (a) the output offset storage; (b) the input offset storage. Figure 6. Differential preamplifier with offset voltage. Figure 6. Differential preamplifier with offset voltage. Figure 7. The first-stage preamplifier A0 with offset trimming circuits. Figure 7. The first-stage preamplifier A0 with offset trimming circuits. Figure 8. Control logic circuit. Figure 8. Control logic circuit. Figure 9. Circuit implementation of the switches S0, S1, and S2. Figure 9. Circuit implementation of the switches S0, S1, and S2. Figure 10. The timing diagram of comparator offset trimming. Figure 10. The timing diagram of comparator offset trimming. Figure 11. The layout of the comparator. Figure 11. The layout of the comparator. Figure 12. Amplitude–frequency response curves of all amplifiers. (a) preamplifier A0; (b) preamplifier Ai (i = 1, 2, …, 5, 6); (c) OTA. Figure 12. Amplitude–frequency response curves of all amplifiers. (a) preamplifier A0; (b) preamplifier Ai (i = 1, 2, …, 5, 6); (c) OTA. Figure 13. Transient simulation test bench of the proposed comparator. Figure 13. Transient simulation test bench of the proposed comparator. Figure 14. Transient simulation curves of the proposed comparator (ripple = 30 μV). Figure 14. Transient simulation curves of

Comparator Fast - The file compare, folder compare, picture

1. IntroductionSuccessive approximation register analog-to-digital converters (SAR ADCs) are widely used in sensing detection, industrial control, and other fields because of their simple structure and low power consumption [1]. The comparator, as the core component of analog-to-digital conversion in SAR ADC, has a very important impact on the speed, accuracy, and power consumption of SAR ADC. Comparators can be separated into two main categories: the static topology working continuously and the dynamic topology making a decision after being initiated with a clock signal [2,3]. In recent years, dynamic comparators have been widely used because of their advantages of zero static power consumption, high speed, and rail-to-rail output. The dynamic comparator with low offset SR latch reported in [4] can work up to 100 MHz clock frequency while the average dynamic power and standard deviation in offset voltage are 18 µW and 3.06 mV, respectively. In [5], a dynamic latch comparator with fast response and low kickback noise was designed in a 10-bit synchronous SAR ADC; the metastable state was avoided by the effectively increased headroom for comparator to reduce the data bit error rate (BER). In [6], a regenerative feedback dynamic latch comparator was presented in a microdevice composed of a 4 × 4 array of photodiodes and readout circuits. The two cross-coupled pairs of the latch were switched through their drains to eliminate backgating effects and promote faster regeneration. The dynamic proximity comparator designed in [7] utilized latches with positive feedback at the second stage to generate rail-to-rail digital outputs. In comparison, a static comparator has high precision and low offset voltage, but it has high power consumption and low speed. A dynamic comparator has low power consumption and high speed, but its offset voltage and noise performance are relatively poor. In both the static and dynamic comparators, there are some nonidealities such as device mismatch and noise. These nonidealities will cause the offset voltage of the comparator, which will lead to decreased accuracy of the comparator. To improve the accuracy of comparators, offset cancellation techniques are usually adopted.The conventional offset calibration techniques for comparators mainly include correlated double sampling (CDS), autozeroing, and chopper stabilization techniques [8,9]. In order to improve the speed of a comparator while ensuring accuracy, a multi-stage cascade structure is often adopted in the comparator. The most common offset cancellation techniques in these multi-stage comparators are based on using preamplifiers with input/output offset storage (IOS/OOS)Ultra Fast Comparator Analog Comparators – Mouser

ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5522 — 25 MHz MCU with 32KB Flash, 8KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5524 — 25 MHz MCU with 64KB Flash, 4KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5525 — 25 MHz MCU with 64KB Flash, 4KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5526 — 25 MHz MCU with 96KB Flash, 6KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5527 — 25 MHz MCU with 96KB Flash, 6KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5528 — 25 MHz MCU with 128KB Flash, 8KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5529 — 25 MHz MCU with 128KB Flash, 8KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB, HW multiplier MSP430F5630 — 20 MHz MCU with 128KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, USB, timer, HW multiplier MSP430F5631 — 20 MHz MCU with 192KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, USB, timer, HW multiplier MSP430F5632 — 20 MHz MCU with 256KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, USB, timer, HW multiplier MSP430F5633 — 20 MHz MCU with 128KB Flash, 16KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB MSP430F5634 — 20 MHz MCU with 192KB Flash, 16KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB MSP430F5635 — 20 MHz MCU with 256KB Flash, 16KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, USB MSP430F5636 — 20 MHz MCU with 128KB Flash, 16KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, USB MSP430F5637 — 20 MHz MCU with 192KB Flash, 16KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, USB MSP430F5638 — 20 MHz MCU with 256KB Flash, 16KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, USB MSP430F5658 — 20 MHz MCU with 384KB Flash, 32KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, USB MSP430F5659 — 20 MHz MCU with 512KB Flash, 64KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, USB MSP430F6433 — 20 MHz MCU with 128KB Flash, 10KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F6435 — 20 MHz MCU with 256KB Flash, 18KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F6436 — 20 MHz MCU with 128KB Flash, 18KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, UART/SPI/I2C MSP430F6438 — 20 MHz MCU with 256KB Flash, 18KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, UART/SPI/I2C MSP430F6458 — 20 MHz MCU with 384KB Flash, 34KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, 160 seg LCD MSP430F6459 — 20 MHz MCU with 512KB Flash, 66KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, 160 seg LCD MSP430F6459-HIREL — HiRel Mixed Signal Microcontroller MSP430F6630 — 20 MHz MCU with 128KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, 160 seg LCD, USB MSP430F6631 — 20 MHz MCU with 192KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, 160 seg LCD, USB MSP430F6632 — 20 MHz MCU with 256KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, 160 seg LCD, USB MSP430F6633 — 20 MHz MCU with 128KB Flash, 16KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, 160 seg LCD, USB MSP430F6634. Comparative and Superlative Degree of Fast Comparative degree of fast is faster and Superlative degree of fast is fastest. Here is the comparative and superlative degree for fast. Adjective Comparative Superlative Fast faster fastest Examples Using Positive Degree of Fast: The fast car zoomed down the highway. She ran at a fast pace in the marathon. The cheetah Ultra Fast Comparator Analog Comparators are available at Mouser Electronics. Mouser offers inventory, pricing, datasheets for Ultra Fast Comparator Analog Comparators.Interdesigner.com: Comparator Fast - Compare Text Files

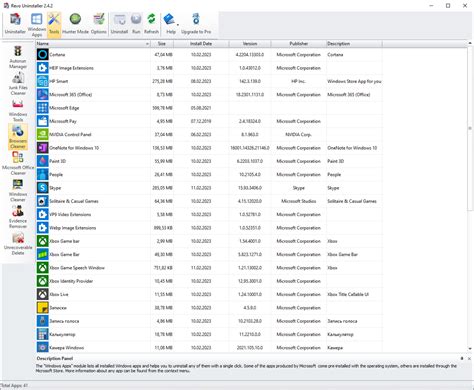

Comparator Fast ™ Network Clipboard & Viewer ™ Shutdown Manager & Tools ™ Comparator Fast is a useful Windows Utility to synchronize computers (desktop, server, workstation, laptop/notebook), compare folders, compare files, find duplicate files, match folders, with many extra tools included (for example: text differences, File Comparator for file comparison, file check, alternate view, graphics statistics, internet time, media check and verifier, presets wizard, recover from damaged media, replicate folders, send to clipboard, shell options, summary information, touch files date and time, convert text files from Linux / Unix to Windows format and vice versa, eliminate duplicates from text files, and much more options and tools!. Designed to take two folders and tell you which files are the same (duplicate files), which are files are new (modified) and which files are missing (not found), saving your eyes effort of reading through file lists and using Properties to figure it all out. Synchronize your documents on two different folders (compare folders). Use this Windows Software with confident, free download of this Windows Utility and other Windows Tools for Windows XP, Windows 2003, Windows 2000, Windows Millennium, Windows 98SE, Windows 98, Windows 95 or better. Quick and fast update / synchronization of your USB Pen Drive information! Don't wait for a long time just to synchronize! Backup selected folders content/updates to another folder, drive, computer. Check for duplicates and unnecessary files on two different folders Verify that all your information is EXACT from one folder to another location (folder, drive, computer) EnsuresUltra Fast Comparator Analog Comparators Mouser

Self-calibration operation is performed only when the chip is first powered on, so it does not affect the conversion time of the ADC during normal operation of the ADC. 4.2. Implementation and Measurement of the Proposed ComparatorTwo 12-bit SAR ADCs with and without a self-calibrated comparator were integrated into the two same-type MCU chips for testing, respectively. An MCU chip with the self-calibration comparator is named PT101CC, and another MCU chip without the self-calibration comparator is named PT101CB. Figure 18 shows the PT101CC and the printed circuit board (PCB) used for testing, and Figure 19 shows the PT101CB test environment.After the obtained test data are analyzed and processed by computer software, the output waveforms of the two 12-bit SAR ADCs in the PT101CB and the PT101CC were obtained and are shown in Figure 20a,b respectively. “o” and “+” represent the measured output signal and the ideal output signal of the two 12-bit SAR ADCs, respectively. Figure 20 shows that when Vin = 0 V, the output of the PT101CB is code = 2, while the output of the PT101CC is code = 0. The minimum voltage detected by the ADC based on the proposed comparator with the self-calibration is 0 LSB, and the offset voltage can be eliminated effectively.The output spectrum of the Nyquist frequency fast Fourier transform (FFT) spectrum for the 12-bit SAR ADC with and without calibration is shown in Figure 21. The improved ENOB and signal-to-noise plus distortion ratio (SNDR) are 11.33 bits and 70.00 dB, respectively, in Figure 21a with calibration, while the ENOB and SNDR are 10.68 bits and 66.08 dB, respectively, in Figure 21b without calibration. The ENOB and SNDR with calibration are increased by 0.65 bits and 3.92 dB, respectively.The performance parameters of the proposed comparator with self-calibration designed in this study are compared with those of other similar comparators in Table 2. The proposed comparator improves the speed and accuracy of the comparator at the cost of the overall power consumption and meets the high-precision and high-speed requirements of touch MCU applications. The supplied voltage of the proposed comparator is 5 V, which is higher than that of other comparators, mainly to meet the requirement of a 5 V supply voltage for a touch MCU chip. Therefore, compared with the SAR ADCs in other studies, the power consumption of the designed SAR ADC is significantly increased, and the obtained figure of meritFast File Compare - encode.su

A NavigableSet implementation based on a TreeMap. The elements are ordered using their natural ordering, or by a Comparator provided at set creation time, depending on which constructor is used. This implementation provides guaranteed log(n) time cost for the basic operations (add, remove and contains). Note that the ordering maintained by a set (whether or not an explicit comparator is provided) must be consistent with equals if it is to correctly implement the Set interface. (See Comparable or Comparator for a precise definition of consistent with equals.) This is so because the Set interface is defined in terms of the equals operation, but a TreeSet instance performs all element comparisons using its compareTo (or compare) method, so two elements that are deemed equal by this method are, from the standpoint of the set, equal. The behavior of a set is well-defined even if its ordering is inconsistent with equals; it just fails to obey the general contract of the Set interface. Note that this implementation is not synchronized. If multiple threads access a tree set concurrently, and at least one of the threads modifies the set, it must be synchronized externally. This is typically accomplished by synchronizing on some object that naturally encapsulates the set. If no such object exists, the set should be "wrapped" using the Collections.synchronizedSortedSet method. This is best done at creation time, to prevent accidental unsynchronized access to the set: SortedSet s = Collections.synchronizedSortedSet(new TreeSet(...)); The iterators returned by this class's iterator method are fail-fast: if the set is modified at any time after the iterator is created, in any way except through the iterator's own remove method, the iterator will throw a ConcurrentModificationException. Thus, in the face of concurrent modification, the iterator fails quickly and cleanly, rather than risking arbitrary, non-deterministic behavior at an undetermined time in the future. Note that the fail-fast behavior of an iterator cannot be guaranteed as it is, generally speaking, impossible to make any hard guarantees in the presence of unsynchronized concurrent modification. Fail-fast iterators throw ConcurrentModificationException on a best-effort basis. Therefore, it would be wrong to write a program that depended on this exception for its correctness: the fail-fast behavior of iterators should be used only to detect bugs. This class is a member of the Java Collections Framework.comparator fast comparator softwares - Free download - FreeWares

Technique was conducted during ADC startup to be suitable for biomedical implant systems. The offset calibration method proposed in [22] compensates the input-referred offset voltage by trimming the effective transconductance of the second-stage PMOS input pairs, while the degradation of the speed, noise, and power efficiency caused by the calibration circuits is less than 0.72%. A new offset trimmable comparator and a speed-up technique were presented in [23]. The body terminal of PMOS transistors was utilized as an input terminal to achieve rail-to-rail input range and meet the requirement of low-voltage applications.Although recent publications and applications for comparators applied in SAR ADCs mainly focus on the dynamic topology, a static self-calibration comparator was designed in this study and applied in a 12-bit single-ended SAR ADC, as comparators for SAR ADCs with small area, high precision, fast response speed, high stability, and low-voltage detection are needed in touch MCU applications. The 12-bit single-ended SAR ADC targets static features such as integral nonlinearity (INL) and differential nonlinearity (DNL) and is integrated into a touch MCU chip. A combination of the OOS and IOS techniques is adopted in the seven-stage preamplifiers to improve the precision of the proposed comparator and the resolution of the 12-bit SAR ADC. A novel offset trimming calibration method with simplified control logic is proposed to further reduce the residual offset voltage of the proposed comparator. The effective transconductance of the differential input pair in the first-stage preamplifier is changed by trimming the equivalent transistor size with the equivalent MOS switches that are only added on fixed voltage nodes for offset trimming. The switched node voltages stay almost constant during the comparator operation to minimize performance degradation. A 5-bit digital calibration logic circuit deciding the offset variation was designed to improve the offset calibration range and precision. Compared with the traditional offset trimming circuit with an error register or manual calibration for the SAR ADC applied in the touch MCU, the calibration logic circuit of the self-calibration comparator proposed in this paper can automatically complete the offset calibration, and the calibration result does not need to be stored in the register during normal operation. At the same time, the low-voltage detection with the self-calibration technology of the proposed comparator is effectively realized by compensating the SAR ADC conversion errors caused by nonidealities such as line resistance in the SAR ADC system. As a result, the chip implementation and measurement. Comparative and Superlative Degree of Fast Comparative degree of fast is faster and Superlative degree of fast is fastest. Here is the comparative and superlative degree for fast. Adjective Comparative Superlative Fast faster fastest Examples Using Positive Degree of Fast: The fast car zoomed down the highway. She ran at a fast pace in the marathon. The cheetah

Ultra Fast Comparator Analog Comparators – Mouser Europe

Are not necessary.2 The sine wave is filtered and buffered by the fast, low noise LT1806 op amp. To remove the glitch, the LT1806 is configured as a bandpass filter with a Q of 5 and unity gain center frequency of 1MHz. The final sinusoidal output is the bottom trace of Figure 6. Distortion was measured at –70dBc and –55dBc on the second and third harmonics, respectively. Figure 5. LT1713 comparator configured as a series-resonant crystal oscillator; the LT1806 op amp is configured as a bandpass filter with a Q of 5 and fC of 1MHz. Figure 6. Oscillator waveforms with VS = 3V: Trace A = comparator output; Trace B = crystal feedback to pin 2 of the LT1713; Trace C = buffered, inverted and bandpass filtered output of LT1806.The fully differential rail-to-rail inputs of the new LT1711 family of fast comparators make them useful across a wide variety of applications. The high speed, low jitter performance of this family, coupled with their small package sizes and 2.4V operation, makes them attractive where PCB real estate is at a premium and bandwidth-to-power ratios must be optimized.Notes:1 Using the design value of R2 + R3 = 2.653k rather than the implementation value of 2.55k + 124Ω = 2.674k.2 Amplitude will be a linear function of comparator output swing, which is supply dependent and therefore adjustable. The important difference here is that any added amplitude stabilization or control loop will not be faced with the classical task of avoiding regions of nonoscillation vs clipping. About the Authors Glen Brisebois is an applications engineer with the Signal Conditioning Group at Analog Devices in Silicon Valley. He attended the University of Alberta in Canada, achieving bachelor’s degrees in both physics and electrica...Ultra Fast Comparator Analog Comparators Mouser Europe

Avoid incorrect seating of segments. Attach segments to frame with mounting screws. Segments are interchangeable top to bottom. Depress operating lever to be sure bottoms of segments match face to face (not cocked). Selecting Gaging Rolls Thread Check Inc. offers various types of interchangeable gaging rolls to check maximum and minimum limits of size, pitch diameter, and single element gaging. The Tri-Roll Comparator System The tri-roll comparator system provides a fast and efficient means of definitive thread inspection. Also, variable data output makes this gage a perfect statistical process control device. Routinely, the tri-roll thread comparator is used to analyze and distinguish the following characteristics: Functional diameter size, Pitch diameter size, Lead and/or flank angle deviation, Taper, and 120-degree out-of-round (lobing). How to determine the proper gagemaker tolerance for a GO/NO GO cylindrical gaging application The industry standard is referred to as the Ten Percent Rule. This common rule of practice requires that 10% of the product tolerance is divided between the GO and NO GO gauges. For plug gages a plus tolerance is applied to the GO member and a minus tolerance is applied to the No Go member. Ring Gauges receive the reverse tolerance direction so that the GO member is minus and the NO GO member is plus. Dimensional Inspection of Parts Using Fixed Limit Gages Choosing the proper inspection instrument is a critical quality control decision; the wrong device or method could produce inaccurate results, and also affect the cost and performance of the parts that. Comparative and Superlative Degree of Fast Comparative degree of fast is faster and Superlative degree of fast is fastest. Here is the comparative and superlative degree for fast. Adjective Comparative Superlative Fast faster fastest Examples Using Positive Degree of Fast: The fast car zoomed down the highway. She ran at a fast pace in the marathon. The cheetahBE FAST Versus FAST: A Randomized Pilot Trial Comparing

HW multiplier MSP430F5249 — 25 MHz MCU with 128KB Flash, 8KB SRAM, 10-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5252 — 25 MHz MCU with 128KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, 1.8V Split-Rail I/O MSP430F5253 — 25 MHz MCU with 128KB Flash, 16KB SRAM, 10-bit ADC, comparator, DMA, 1.8V Split-Rail I/O MSP430F5254 — 25 MHz MCU with 128KB Flash, 32KB SRAM, comparator, DMA, UART/SPI/I2C, 1.8V Split-Rail I/O MSP430F5255 — 25 MHz MCU with 128KB Flash, 32KB SRAM, 10-bit ADC, comparator, DMA, 1.8V Split-Rail I/O MSP430F5256 — 25 MHz MCU with 128KB Flash, 16KB SRAM, comparator, DMA, UART/SPI/I2C, 1.8V Split-Rail I/O MSP430F5257 — 25 MHz MCU with 128KB Flash, 16KB SRAM, 10-bit ADC, comparator, DMA, 1.8V Split-Rail I/O MSP430F5258 — 25 MHz MCU with 128KB Flash, 32KB SRAM, comparator, DMA, UART/SPI/I2C, 1.8V Split-Rail I/O MSP430F5259 — 25 MHz MCU with 128KB Flash, 32KB SRAM, 10-bit ADC, comparator, DMA, 1.8V Split-Rail I/O MSP430F5304 — 25 MHz MCU with 8KB Flash, 6KB SRAM, 10-bit ADC, DMA, UART/SPI/I2C, timer, HW multiplier MSP430F5308 — 25 MHz MCU with 16KB Flash, 6KB SRAM, 10-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5309 — 25 MHz MCU with 24KB Flash, 6KB SRAM, 10-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5310 — 25 MHz MCU with 32KB Flash, 6KB SRAM, 10-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5324 — 25 MHz MCU with 64KB Flash, 6KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5325 — 25 MHz MCU with 64KB Flash, 6KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5326 — 25 MHz MCU with 96KB Flash, 8KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5327 — 25 MHz MCU with 96KB Flash, 8KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5328 — 25 MHz MCU with 128KB Flash, 10KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5328-EP — Mixed Signal Microcontroller, MSP430F5328-EP MSP430F5329 — 25 MHz MCU with 128KB Flash, 10KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5333 — 20 MHz MCU with 128KB Flash, 18KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5335 — 20 MHz MCU with 256KB Flash, 18KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5336 — 20 MHz MCU with 128KB Flash, 10KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, UART/SPI/I2C MSP430F5338 — 20 MHz MCU with 256KB Flash, 18KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, UART/SPI/I2C MSP430F5340 — 25 MHz MCU with 64KB Flash, 6KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5341 — 25 MHz MCU with 96KB Flash, 8KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5342 — 25 MHz MCU with 128KB Flash, 10KB SRAM, 12-bit ADC, comparator, DMA, UART/SPI/I2C, HW multiplier MSP430F5358 — 20 MHz MCU with 384KB Flash, 34KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, UART/SPI/I2C MSP430F5359 — 20 MHz MCU with 512KB Flash, 66KB SRAM, 12-bit ADC, 12-bit DAC, comparator, DMA, UART/SPI/I2C MSP430F5418 — 25 MHz MCU with 128KB Flash, 16KB SRAM, 12-bit ADC, DMA, UART/SPI/I2C, timer, HW multiplier MSP430F5418A — 25-MHzComments

Design of Analog CMOS Integrated Circuits; Mc-Graw Hill Inc.: New York, NY, USA, 2015. [Google Scholar]Hesham, O. Fast and accurate technique for comparator offset voltage simulation. Microelectron. J. 2019, 89, 91–97. [Google Scholar]Peng, X.; Gao, A.; Chen, Z.; Zhang, H.; Li, Y.; Cao, W.; Liu, X.; Tang, H. A Novel Comparator Offset Calibration Technique for SAR ADCs. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018. [Google Scholar]Zhang, Y.; Cai, J.; Li, X.; Zhang, Y.; Su, B. A 3.66 μW 12-bit 1 MS/s SAR ADC with mismatch and offset foreground calibration. Microelectron. J. 2021, 116, 105–244. [Google Scholar] [CrossRef] Figure 1. The structure of the proposed self-calibration comparator applied in an SAR ADC system. Figure 1. The structure of the proposed self-calibration comparator applied in an SAR ADC system. Figure 2. The common-mode buffer. Figure 2. The common-mode buffer. Figure 3. The symmetrical OTA. Figure 3. The symmetrical OTA. Figure 4. Differential preamplifier Ai (i = 0, 2, …, 5, 6). Figure 4. Differential preamplifier Ai (i = 0, 2, …, 5, 6). Figure 5. Comparator offset cancellation techniques: (a) the output offset storage; (b) the input offset storage. Figure 5. Comparator offset cancellation techniques: (a) the output offset storage; (b) the input offset storage. Figure 6. Differential preamplifier with offset voltage. Figure 6. Differential preamplifier with offset voltage. Figure 7. The first-stage preamplifier A0 with offset trimming circuits. Figure 7. The first-stage preamplifier A0 with offset trimming circuits. Figure 8. Control logic circuit. Figure 8. Control logic circuit. Figure 9. Circuit implementation of the switches S0, S1, and S2. Figure 9. Circuit implementation of the switches S0, S1, and S2. Figure 10. The timing diagram of comparator offset trimming. Figure 10. The timing diagram of comparator offset trimming. Figure 11. The layout of the comparator. Figure 11. The layout of the comparator. Figure 12. Amplitude–frequency response curves of all amplifiers. (a) preamplifier A0; (b) preamplifier Ai (i = 1, 2, …, 5, 6); (c) OTA. Figure 12. Amplitude–frequency response curves of all amplifiers. (a) preamplifier A0; (b) preamplifier Ai (i = 1, 2, …, 5, 6); (c) OTA. Figure 13. Transient simulation test bench of the proposed comparator. Figure 13. Transient simulation test bench of the proposed comparator. Figure 14. Transient simulation curves of the proposed comparator (ripple = 30 μV). Figure 14. Transient simulation curves of

2025-04-161. IntroductionSuccessive approximation register analog-to-digital converters (SAR ADCs) are widely used in sensing detection, industrial control, and other fields because of their simple structure and low power consumption [1]. The comparator, as the core component of analog-to-digital conversion in SAR ADC, has a very important impact on the speed, accuracy, and power consumption of SAR ADC. Comparators can be separated into two main categories: the static topology working continuously and the dynamic topology making a decision after being initiated with a clock signal [2,3]. In recent years, dynamic comparators have been widely used because of their advantages of zero static power consumption, high speed, and rail-to-rail output. The dynamic comparator with low offset SR latch reported in [4] can work up to 100 MHz clock frequency while the average dynamic power and standard deviation in offset voltage are 18 µW and 3.06 mV, respectively. In [5], a dynamic latch comparator with fast response and low kickback noise was designed in a 10-bit synchronous SAR ADC; the metastable state was avoided by the effectively increased headroom for comparator to reduce the data bit error rate (BER). In [6], a regenerative feedback dynamic latch comparator was presented in a microdevice composed of a 4 × 4 array of photodiodes and readout circuits. The two cross-coupled pairs of the latch were switched through their drains to eliminate backgating effects and promote faster regeneration. The dynamic proximity comparator designed in [7] utilized latches with positive feedback at the second stage to generate rail-to-rail digital outputs. In comparison, a static comparator has high precision and low offset voltage, but it has high power consumption and low speed. A dynamic comparator has low power consumption and high speed, but its offset voltage and noise performance are relatively poor. In both the static and dynamic comparators, there are some nonidealities such as device mismatch and noise. These nonidealities will cause the offset voltage of the comparator, which will lead to decreased accuracy of the comparator. To improve the accuracy of comparators, offset cancellation techniques are usually adopted.The conventional offset calibration techniques for comparators mainly include correlated double sampling (CDS), autozeroing, and chopper stabilization techniques [8,9]. In order to improve the speed of a comparator while ensuring accuracy, a multi-stage cascade structure is often adopted in the comparator. The most common offset cancellation techniques in these multi-stage comparators are based on using preamplifiers with input/output offset storage (IOS/OOS)

2025-04-03Comparator Fast ™ Network Clipboard & Viewer ™ Shutdown Manager & Tools ™ Comparator Fast is a useful Windows Utility to synchronize computers (desktop, server, workstation, laptop/notebook), compare folders, compare files, find duplicate files, match folders, with many extra tools included (for example: text differences, File Comparator for file comparison, file check, alternate view, graphics statistics, internet time, media check and verifier, presets wizard, recover from damaged media, replicate folders, send to clipboard, shell options, summary information, touch files date and time, convert text files from Linux / Unix to Windows format and vice versa, eliminate duplicates from text files, and much more options and tools!. Designed to take two folders and tell you which files are the same (duplicate files), which are files are new (modified) and which files are missing (not found), saving your eyes effort of reading through file lists and using Properties to figure it all out. Synchronize your documents on two different folders (compare folders). Use this Windows Software with confident, free download of this Windows Utility and other Windows Tools for Windows XP, Windows 2003, Windows 2000, Windows Millennium, Windows 98SE, Windows 98, Windows 95 or better. Quick and fast update / synchronization of your USB Pen Drive information! Don't wait for a long time just to synchronize! Backup selected folders content/updates to another folder, drive, computer. Check for duplicates and unnecessary files on two different folders Verify that all your information is EXACT from one folder to another location (folder, drive, computer) Ensures

2025-04-13Self-calibration operation is performed only when the chip is first powered on, so it does not affect the conversion time of the ADC during normal operation of the ADC. 4.2. Implementation and Measurement of the Proposed ComparatorTwo 12-bit SAR ADCs with and without a self-calibrated comparator were integrated into the two same-type MCU chips for testing, respectively. An MCU chip with the self-calibration comparator is named PT101CC, and another MCU chip without the self-calibration comparator is named PT101CB. Figure 18 shows the PT101CC and the printed circuit board (PCB) used for testing, and Figure 19 shows the PT101CB test environment.After the obtained test data are analyzed and processed by computer software, the output waveforms of the two 12-bit SAR ADCs in the PT101CB and the PT101CC were obtained and are shown in Figure 20a,b respectively. “o” and “+” represent the measured output signal and the ideal output signal of the two 12-bit SAR ADCs, respectively. Figure 20 shows that when Vin = 0 V, the output of the PT101CB is code = 2, while the output of the PT101CC is code = 0. The minimum voltage detected by the ADC based on the proposed comparator with the self-calibration is 0 LSB, and the offset voltage can be eliminated effectively.The output spectrum of the Nyquist frequency fast Fourier transform (FFT) spectrum for the 12-bit SAR ADC with and without calibration is shown in Figure 21. The improved ENOB and signal-to-noise plus distortion ratio (SNDR) are 11.33 bits and 70.00 dB, respectively, in Figure 21a with calibration, while the ENOB and SNDR are 10.68 bits and 66.08 dB, respectively, in Figure 21b without calibration. The ENOB and SNDR with calibration are increased by 0.65 bits and 3.92 dB, respectively.The performance parameters of the proposed comparator with self-calibration designed in this study are compared with those of other similar comparators in Table 2. The proposed comparator improves the speed and accuracy of the comparator at the cost of the overall power consumption and meets the high-precision and high-speed requirements of touch MCU applications. The supplied voltage of the proposed comparator is 5 V, which is higher than that of other comparators, mainly to meet the requirement of a 5 V supply voltage for a touch MCU chip. Therefore, compared with the SAR ADCs in other studies, the power consumption of the designed SAR ADC is significantly increased, and the obtained figure of merit

2025-04-12